Mundarija:

- 1 -qadam: Blok diagrammasi

- 2 -qadam: ishlash printsipi

- 3 -qadam: Mantiqni amalga oshirish

- 4 -qadam: Qulfni hal qilish

- 5 -qadam: Qurilma konfiguratsiyasi - Matrix0 sxemasi

- 6 -qadam: Qurilma konfiguratsiyasi - SPI Clocking Logic

- 7 -qadam: Qurilma konfiguratsiyasi - Matrix0 komponentlarining xususiyatlari

- 8 -qadam: Qurilma konfiguratsiyasi - Matrix1 sxemasi

- 9 -qadam: Qurilma konfiguratsiyasi - 3 -bitli ikkilik hisoblagich

- 10 -qadam: Qurilma konfiguratsiyasi - 3 -bitli mantiqni solishtiring

- 11 -qadam: Qurilma konfiguratsiyasi - raqamli taqqoslash mantig'i va vaqtinchalik ro'yxatga olish

- 12 -qadam: Qurilma konfiguratsiyasi - Matrix1 komponentlarining xususiyatlari

- 13 -qadam: Natijalar

- Muallif John Day day@howwhatproduce.com.

- Public 2024-01-30 13:24.

- Oxirgi o'zgartirilgan 2025-01-23 15:14.

Boshqaruv tizimlari va tegishli qurilmalar bir nechta quvvat manbalari, masalan, noto'g'ri chiziqlar yoki batareyalar bilan shug'ullanadi va ma'lum bir to'plam orasida eng yuqori (yoki eng past) chiziqni kuzatishi kerak.

Masalan, "ko'p batareyali" quvvatli tizimda yukni almashtirish tizimdan batareyalar massividagi minimal yoki maksimal kuchlanishni (max yoki ma'lum kommutatsiya algoritmining funktsiyasi sifatida) kuzatishni va yukni dinamik ravishda yo'naltirishni talab qiladi. real vaqtda eng mos manba. Shu bilan bir qatorda, to'g'ri zaryadlash uchun tizim eng past kuchlanishli batareyani vaqtincha o'chirib qo'yishi mumkin.

Yana bir misol - zamonaviy quyosh energiyasi tizimi, bu erda har bir quyosh paneli tiltrotat mexanizmi va quyoshni kuzatish sxemasi bilan jihozlangan (ikkinchisi panelni yo'naltirish uchun Quyoshning joylashuvi to'g'risida ma'lumot beradi). Maksimal kuchlanish ma'lumoti bilan, quyosh panelining har bir pozitsiyasi, eng yuqori chiqish voltajini etkazib beradigan simlar paneli asosida aniq sozlanishi mumkin, shu bilan quvvatni optimallashtirishning yuqori darajasiga erishiladi.

Tijorat IClarning (asosan mikrokontrollerlar) bir nechta markalari mavjud bo'lib, ular asosan maksimal kuchlanish kuzatuvchisini amalga oshirishi mumkin. Biroq, ular dasturlashni talab qiladi va aralash signalli echimdan ko'ra iqtisodiy jihatdan kamroq. Dialog GreenPAK ™ dizaynini to'ldirish dizaynning arzonligi, o'lchami va modulligiga ijobiy ta'sir ko'rsatishi mumkin. Ushbu dizayn analog va raqamli sxemalarni bitta chipga birlashtirishning afzalliklaridan foydalanadi.

Ushbu yo'riqnomada sakkizta alohida manbalar orasida maksimal (yoki oxir-oqibat) kuchlanish o'lchagichni amalga oshirish uchun zarur bo'lgan analog va raqamli mantiq amalga oshiriladi.

8-kanalli analog max/min kuchlanishli monitorni amalga oshirish uchun SLG46620G ishlatiladi.

Quyida biz 8 kanalli analog max/min kuchlanishli monitorni yaratish uchun yechim qanday dasturlashtirilganligini tushunish uchun zarur bo'lgan qadamlarni tasvirlab berdik. Ammo, agar siz dasturlash natijasini olishni xohlasangiz, GreenPAK dasturini yuklab oling va tugallangan GreenPAK dizayn faylini ko'ring. GreenPAK Development Kit-ni kompyuteringizga ulang va 8 kanalli analog max/min kuchlanish monitorini yaratish uchun dasturni bosing.

1 -qadam: Blok diagrammasi

1 -rasmda joriy qilingan tizimning global diagrammasi ko'rsatilgan.

8 tagacha o'zgaruvchan kuchlanish manbalaridan tashkil topgan tarmoq, boshqalarga nisbatan eng yuqori kuchlanishli manbani tanlashga qodir bo'lgan ichki dizaynga ulangan GreenPAK ADC moduliga ulanadi. Ichki mantiq bu ma'lumotlarni ko'rsatish yoki keyingi ishlov berish uchun chiqaradi.

Dizayn GreenPAK SLG46620G mahsulotiga asoslangan, chunki u dastur uchun zarur bo'lgan barcha analog va raqamli qurilish bloklarini o'z ichiga oladi. Bu amalga oshirishda, massiv to'g'ridan -to'g'ri GreenPAK IC tomonidan boshqariladigan ADG508 analog multipleksor yordamida skanerdan o'tkaziladi.

Chiqish ma'lumoti-maksimal kuchlanishdagi kuchlanish manbai raqamiga mos keladigan 3-bitli raqamli raqam. Ushbu ma'lumotni olishning to'g'ridan-to'g'ri usuli-bu raqamni 7 segmentli displey yordamida ko'rsatish. Buni SLG46620G raqamli chiqishini 7-segmentli displey drayveriga, masalan, Referatsiyada tasvirlangan GreenPAK eritmasi yoki 74LS47 IC-ga ulash orqali osonlikcha bajarish mumkin.

Taqdim etilgan sxema maksimal kuchlanishni qidiradi. Dizaynni minimal voltli topgichga aylantirish uchun analog multipleksor va GreenPAK analogli kirish o'rtasida multipleksor chiqishini 1 V mos yozuvlar kuchlanishidan chiqarib, oddiy konditsioner sxemani qo'shish kerak.

2 -qadam: ishlash printsipi

Dizayn maksimal kuchlanishli manbani tanlashni maqsad qiladi, shuning uchun skanerlash butun massivda o'tkaziladi, shu bilan birga oxirgi maksimal qiymat saqlanadi va uni kirishdagi keyingi qiymat bilan solishtiriladi (u skanerlashda keyingi kuchlanish manbaiga tegishli).

Quyida biz "kirish" yoki "pastadir" sifatida barcha kirishlar bo'yicha to'liq ko'paytirish ketma -ketligini ko'rib chiqamiz.

Ikkala qiymatni taqqoslash ACMP komponentlari yordamida amalga oshirilmaydi (lekin SLG46620G -da mavjud), aksincha qiymatlar raqamlashtirilgandan so'ng DCMP moduli orqali. Bu ilg'or va takomillashtirilgan texnik bo'lib, birinchi bo'lib Reference -da ko'rib chiqilgan.

2 -rasmda SLG46620G bu dizayn uchun qanday tuzilganligi ko'rsatilgan.

Analog kirish signali ADC kirishiga PGA komponenti orqali 1 ga teng daromad oladi. Har xil daromad parametrlari, kirish voltajini 0-1 V ga moslashtirishga mo'ljallangan, oldingi konditsioner elektronika bilan eng yaxshi moslikni topish mumkin. GreenPAK ADC moduli diapazoni.

ADC bir martalik rejimda ishlaydi va analog signalni 8-bitli raqamli kodga o'zgartiradi, keyin esa DCMP moduliga o'tkaziladi. Raqamli kod ADC/FSM buferi sifatida tuzilgan SPI blokiga ham yuboriladi, bu erda raqamli kod saqlanishi mumkin va SPI CLK kirishiga keyingi zarba kelguncha o'zgarmaydi. E'tibor bering, maxsus mantiqiy blok SPI CLK kirishini boshqaradi. Bu qismni keyinroq o'rganamiz, chunki bu to'g'ri ishlash uchun javob beradigan "asosiy" mantiq. Yangi raqamli kod SPI modulida saqlanadi, agar u haqiqiy maksimal kirish voltajiga tegishli bo'lsa.

DCMP komponenti joriy ADC ma'lumotlarini SPI blokida saqlangan oxirgi g'olib bilan (oxirgi topilgan maksimal) solishtirish uchun ishlatiladi. Yangi ADC ma'lumotlari avvalgisidan kattaroq bo'lganda, OUT+ chiqishida puls hosil qiladi. Biz OUT+ signalidan SPI blokini yangi g'olib bilan yangilash uchun foydalanamiz.

Global soat signallari ADC konvertatsiyasini va umumiy vaqtni boshqaradi. O'tkazish amalga oshirilgandan so'ng, ADC parallel chiqish chiqishi bilan o'z vaqtida muvofiqlashtirilgan ADC ning chiqish signal pulslari. Biz Matrix1da DFFlar tomonidan amalga oshiriladigan 3-bitli ikkilik hisoblagichni ko'paytirish uchun ham INT chiqishini ishlatamiz, bu uchta sababga ko'ra foydalidir:

1. Hisoblagich chiqish liniyalari tashqi analog multipleksorga murojaat qiladi, shu bilan ADCga keyingi kirish kuchlanishi xizmat qiladi;

2. Hisoblash vaqtinchalik g'olibni skanerlash vaqtida saqlash uchun 3-bitli registrga (Matrix1-da joriy qilingan) joylashtirilgan;

3. Skanerlash tugallangach, ikkinchi 3-bitli registrni (Matrix0 da joriy qilingan) yangilash uchun hisob ochiladi.

3 -qadam: Mantiqni amalga oshirish

ADC moduli ketma -ket barcha kirish voltajlarining konvertatsiya qilingan ma'lumotlarini birin -ketin, noma'lum muddatga taqdim etadi. Multiplexerga 0b111 (o'nlik kasr 7) manzili berilgach, hisoblagich 0b000 (o'nlik kasr 0) ga o'tadi va shu tariqa kirish kuchlanishlarini yangi skanerlashni boshlaydi.

Tekshirish paytida, parallel ma'lumotlar chiqishi to'g'ri bo'lganda, ADC INT chiqish signali hosil bo'ladi. Bu signal zarba berganda, analog multipleksor PGA ga mos keladigan kuchlanishni ta'minlab, keyingi kirishga o'tishi kerak. Shuning uchun ADC INT chiqishi 2-rasmning 3-bitli ikkilik hisoblagichining to'g'ridan-to'g'ri signalidir, uning 3-bitli parallel chiqish so'zi tashqi analog multipleksorga to'g'ridan-to'g'ri murojaat qiladi (1-rasmda "V tanlash").

Keling, kirish kuchlanishlari quyidagi munosabatlarga ega bo'lishi kerak bo'lgan misolga murojaat qilaylik:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

3-rasmda maksimal qaror qabul qilish mexanizmida ishtirok etuvchi asosiy signallar ko'rsatilgan.

Ma'lumotlar oxir -oqibat SPI tampon registriga INT pulslari bilan bir vaqtda kiritilgandan so'ng, SPI buferi tarkibi keyingi ADC konvertatsiya natijasi bilan taqqoslanadigan taqqoslash oynasi mavjud. Bu aniq vaqt DCMP chiqishida OUT+ pulslarini hosil qilishiga olib keladi. Biz SPI bufer registriga yangi qiymatlarni yuklash uchun bu pulslardan foydalanishimiz mumkin.

Oldingi rasmdagi SPI bufer ma'lumotlar liniyasidan ko'rinib turibdiki, SPI registri har doim 8 kirishning eng katta qiymatini o'z ichiga oladi va u faqat DCMP moduli tomonidan katta qiymat aniqlanganda yangilanadi (DCMP OUT+ chiqish chizig'i, etishmayotgan impulslar V2ni V5 bilan solishtirmaguncha registrda saqlanib qolishiga olib keladi).

4 -qadam: Qulfni hal qilish

Agar amalga oshirilgan mantiq yuqorida aytib o'tilganidek bo'lsa, biz aniq vaziyatga tushib qolishimiz aniq: tizim SPI bufer registrida saqlanganidan mos keladigan kuchlanishni aniqlay oladi.

Agar bu kuchlanish pasayib ketsa va shu paytgacha undan pastroq bo'lgan boshqa kirish eng yuqori bo'lsa, u hech qachon aniqlanmaydi. Bu holat 4 -rasmda yaxshiroq tushuntiriladi, bu erda faqat 3 ta kirish voltaji mavjud. aniqlik.

2 -takrorlash paytida V3 tushadi va V1 haqiqiy maksimal kuchlanishdir. Lekin DCMP moduli pulsni ta'minlamaydi, chunki SPI bufer registrida saqlangan ma'lumotlar (0,6 V ga to'g'ri keladi) V1 (0,4 V) mos keladiganidan katta.

Keyin tizim "mutlaq" maksimal topuvchi vazifasini bajaradi va chiqishni to'g'ri yangilamaydi.

Bu muammoni hal qilishning eng yaxshi usuli, tizim barcha kanallarning to'liq so'rovnomasini yakunlagach, ma'lumotlarni SPI buferlar reestriga qayta yuklashga majburlashdir.

Aslida, agar bu kirishda kuchlanish hali ham eng yuqori bo'lsa, hech narsa o'zgarmaydi va boshqaruv xavfsiz tarzda davom etadi (yuqoridagi 4 -rasmga qarang, bu 0 va 1 -chi tsikllarni takrorlash holatidir). Boshqa tomondan, agar bu kirishda tasodifan kuchlanish boshqa kirishdan pastroq qiymatga tushsa, qiymatni qayta yuklash DCMP moduliga yangi maksimal qiymat bilan solishtirganda OUT+ pulsini ishlab chiqarish imkoniyatini beradi. 2 va 3 -sonli tsikllarni takrorlash hollari).

Muammoni bartaraf etish uchun mantiqiy sxemaning bir qismi zarur. Haqiqiy maksimal kirishga yetganda SPI komponentiga soat signalini berishi kerak, shuning uchun SPI bufer registriga yangilangan ma'lumotlar so'zini qayta yuklashga majbur qiladi. Bu 7.2 va 7.6 -bo'limlarda muhokama qilinadi.

5 -qadam: Qurilma konfiguratsiyasi - Matrix0 sxemasi

SLG46620G 2 -rasmda tasvirlangan ikkita Matritsa blokiga ega. Quyidagi rasmlarda mos keladigan qurilma konfiguratsiyasi ko'rsatilgan.

O'chirishning yuqori qismi - 3 ta DFF (DFF0, DFF1 va DFF2) yordamida amalga oshiriladigan "Loop Register". 7-segmentli displey haydovchisiga "g'olib" ning ikkilik raqamini yuborish uchun kirish multipleksorining har bir tsiklidan so'ng yangilanadi, bu oxirgi skanerlashda eng yuqori kuchlanishli kirish. DFF -lar uchun soat ham, ma'lumotlar ham P12, P13, P14 va P15 portlari orqali Matrix1 -da amalga oshirilgan mantiqdan kelib chiqadi.

Pastki qism - analog old uchi, 8 -pinli kirish va PGA - daromad x1. ADC INT chiqishi SPI -ning soat mantig'iga ham, Matrix1 -ga P0 porti orqali o'tadi, bu erda u hisoblagich uchun soat signali bo'lib xizmat qiladi.

ADC va SPI parallel ma'lumotlar chiqishlari Matrix1da DCMP komponentiga ulanishi uchun mos ravishda NET11 va NET15 deb belgilanadi.

6 -qadam: Qurilma konfiguratsiyasi - SPI Clocking Logic

"Mantiqni amalga oshirish" bo'limida ilgari aytib o'tilganidek, har safar SPI buferlar reestri yangilanadi, chunki haqiqiy saqlangan qiymat va yangi ADC konvertatsiya ma'lumotlari o'rtasidagi taqqoslash DCMP OUT+ chiqishida impuls hosil qiladi.

Agar signal ADC INT chiqishi bilan AND-tahrir qilinsa, signal yaxlitligi ta'minlanadi. Bu har qanday burilish va noto'g'ri qo'zg'alishni oldini oladi.

Shuningdek, biz tanglik holatlarini o'tkazib yubormaslik uchun, SPI buferi tsikl g'olibning haqiqiy ma'lumotlariga etib kelganida yangilanishi kerakligini ta'kidladik.

O'yinda SPIni to'g'ri aniqlash uchun uchta signal mavjud:

1. ADC INT chiqishi (LUT0-IN1)

2. DCMP OUT+ chiqishi (PUT port orqali LUT0-IN0)

3. Hisoblash Latch signaliga teng (P11 port orqali LUT0-IN2)

Dastlabki ikkitasi AND-ed va ikkalasi ORUT-LUT0 da, ikkinchisi esa 6-rasmda ko'rsatilganidek konfiguratsiya qilingan.

7 -qadam: Qurilma konfiguratsiyasi - Matrix0 komponentlarining xususiyatlari

7-10-rasmlarda Matrix0 ga tegishli qolgan qolgan oynali oynalar ko'rsatilgan.

8 -qadam: Qurilma konfiguratsiyasi - Matrix1 sxemasi

9 -qadam: Qurilma konfiguratsiyasi - 3 -bitli ikkilik hisoblagich

Zanjirning yuqori qismida mantiqiy elementlar, asosan ADC INT chiqishi bilan ishlangan 3-bitli ikkilik hisoblagich mavjud. Bu hisoblagich 12 -rasmda ko'rsatilgan "standart" sxemasi bilan amalga oshiriladi.

Bu hisoblagich bizning dizaynimizda Flip-Flops DFF9, DFF10, DFF11 va INV1, LUT4, LUT8 yordamida amalga oshiriladi. DFF9 chiqishi LSB, DFF11 esa 13 -rasmda ko'rsatilgandek MSB.

LUT4 XOR sifatida tuzilgan, LUT8 esa 12-rasmdagi AND-XOR mantig'ini bajaradi.

Hisoblagichning chiqishlari analog analog multipleksorga murojaat qilish uchun uchta raqamli chiqish piniga o'tadi.

LUT10 skaner tugagandan so'ng hisoblagich kodini ochadi va zarbani Matrix0 ga DLY8 va P12 porti orqali uzatadi. Bu hisoblagichning chiqishlarini AND-kiritish orqali amalga oshiriladi, shuning uchun 7-sonli raqamni (0b111 ikkilik, pastadir oxiri) dekodlash.

10 -qadam: Qurilma konfiguratsiyasi - 3 -bitli mantiqni solishtiring

15 -rasmda "g'olib" ning joriy manzilida pastadir takrorlanishini aniqlash uchun ishlatiladigan sxema ko'rsatilgan. Bunday holda, yuqorida aytib o'tilganidek, raqamli zarba, mumkin bo'lgan tiqilib qoladigan vaziyatni hal qilish uchun joriy ADC natijasini qayta yuklashga majbur qilishi kerak.

"G'olib" manzili Matrix1 vaqtinchalik registrida saqlanadi (pastga qarang), joriy manzil esa ikkilik hisoblagich orqali chiqariladi.

XNOR eshiklari har ikkala kirish teng bo'lganda haqiqiy (mantiq 1 yoki "yuqori") chiqishni ta'minlaydi. VA-signalini barcha bitlar uchun (LUT9) ikkala ikkilik kod bir xil bo'lganida bizga puls beradi. Paritetni tekshiruvchi sifatida XOR eshiklari haqida tafsilotlarni Ma'lumotnomada topish mumkin.

"Counter-equals-Latch" signali Matrix0 ga P11 porti orqali uzatiladi.

11 -qadam: Qurilma konfiguratsiyasi - raqamli taqqoslash mantig'i va vaqtinchalik ro'yxatga olish

11-rasmning pastki qismida (16-rasmda ta'kidlangan) DCMP bloki ko'rsatilgan, bu dizaynning qaror qabul qilish qismi.

DFF6, 7 va 8 3-bitli registrni shakllantiradi, bu esa "g'olib" vaqtinchalik kiruvchi raqamini saqlashga yordam beradi. Flip-floplarga kirish-bu aniqlik uchun o'tkazib yuborilgan 11-rasmning global Matrix1 sxemasida ko'rinadigan 3-bitli ikkilik hisoblagichlar.

Ushbu registrning chiqishlari 7 segmentli displeyni to'g'ridan-to'g'ri boshqarolmaydi, chunki bu erda saqlangan qiymat skanerlash paytida o'zgaradi va uni skanerlash oxirida "haqiqiy" deb hisoblash kerak.

Shu sababli, vaqtinchalik ro'yxatga olish chiqishlari Matrix0 ning Loop Registriga matritsalararo P13, P14 va P15 portlari orqali ulanadi.

16-rasmda ADC-SPI registrlari taqqoslash natijasida yangi max topilganda, vaqtinchalik registr DCMP OUT+ chiqishi bilan soatlab turishini kuzatish kerak.

Xuddi shu OUT+ signali Matrix0, SPI CLK Logicga P10 port orqali uzatiladi.

12 -qadam: Qurilma konfiguratsiyasi - Matrix1 komponentlarining xususiyatlari

17-19-rasmlarda Matrix1 ga tegishli komponentlar oynalari ko'rsatilgan.

13 -qadam: Natijalar

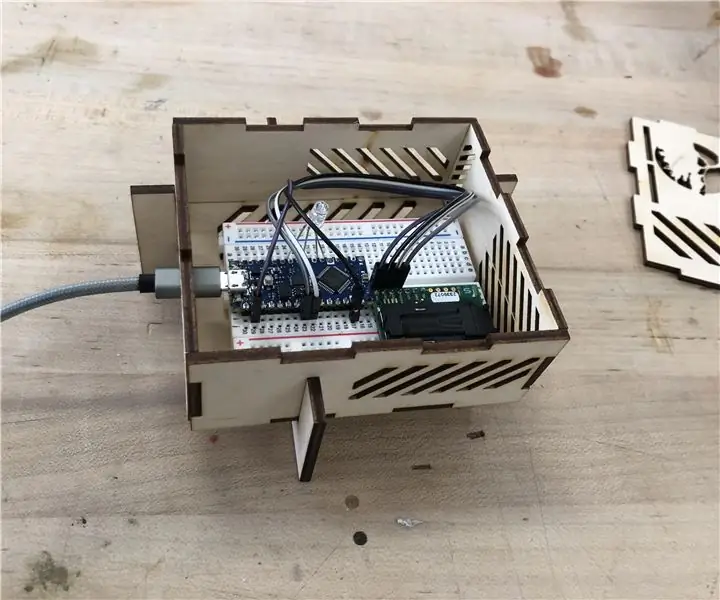

Amalga oshirishni sinab ko'rish uchun baholash taxtasi prototipi tuzilgan, u erda 8 ta analog kirish voltaji TrimPots bilan bir qator rezistorlar bo'linishi orqali olinadi (20 -rasmda ko'rsatilgan).

Qo'llaniladigan multipleksor ADG508 bo'lib, uning qismi bitta quvvat manbai (12 V) bilan ishlashi mumkin.

7 segmentli displey drayveri-74LS47. U parallel kirish so'zini ochadi va 7-segmentli umumiy anodli displeyni boshqaradi.

Baholash taxtasida 21-rasmda ko'rsatilgandek, kengaytirish ulagichida to'g'ridan-to'g'ri GreenPAK Advanced Development Platform-ga ulanadigan 2x10 to'g'ri burchakli ulagich mavjud.

GreenPAK Advanced Development Platform bilan birgalikda tezkor tekshirish uchun signallarni o'lchashni osonlashtiradi. Masalan, 22 -rasmda HP 54620A Logic Analyzer tomonidan olingan signallar to'plami (mos ravishda CLOCK, ADC INT chiqishi va DCMP OUT+ chiqishi) ko'rsatilgan. To'lqin shakllari OUT+ signalining ("A> B" yorlig'i bo'yicha) ko'tarilishining chekkasidan kelib chiqadi, shuning uchun bu analog kirishlar orasida yangi maksimal kuchlanish aniqlanganda to'lqin shaklini olishdir. Aslida, bu 22 -rasmda ko'rsatilgan mos keladigan kuchlanishni oshirish uchun baholash kengashining TrimPots -dan birini aylantirish orqali olingan.

23 -rasmda baholash kengashining sxemasi ko'rsatilgan.

Xulosa

Ushbu yo'riqnomada biz ko'p kanalli boshqaruv tizimlariga umumiy qo'shimcha sifatida ishlatilishi mumkin bo'lgan sakkiz kanalli maksimal (yoki min) kuchlanish o'lchagichni ishga tushirdik. Taqdim etilgan yondashuv GreenPAK komponentlarining ilg'or xususiyatlaridan foydalanadi va qanday qilib bitta chipli analog va raqamli funktsiyalarni birlashtirish mumkinligini ko'rsatadi. Bir nechta tijorat IC -larni Dialog GreenPAK bilan almashtirish mumkin, shunda dastur hajmi va narxini pasaytirish mumkin.

Tavsiya:

USB, FLASHLIGHT, KOMPONENT TESTER VA QO'RILGAN Zaryadlovchiga ega portativ MINI ko'p kuchlanishli PSU: 6 qadam

USB, FLASHLIGHT, KOMPONENT TESTER VA QO'RILGAN Zaryadlovchiga ega portativ MINI MULTI VOLTAGE PSU: Mening birinchi ko'rsatmali qurilmamga xush kelibsiz! Bu ko'rsatma yordamida siz quyosh energiyasidan qimmat bo'lmagan bankni (qo'shimcha qismlar bilan) foydali narsaga aylantira olasiz. Siz har kuni ishlatishingiz mumkin bo'lgan narsa, men kabi, chunki uni ishlatish juda zo'r! Ko'pchilik av

Yuqori kuchlanishli batareyalar uchun kuchlanish monitor: 3 qadam (rasmlar bilan)

Yuqori kuchlanishli batareyalar uchun kuchlanish o'lchagichi: Ushbu qo'llanmada men sizga elektr panelim uchun batareyaning kuchlanish monitorini qanday qurganimni tushuntiraman. Uni xohlagancha o'rnating va batareyangizga faqat ikkita simni ulang (Gnd va Vcc). Ushbu qo'llanmada sizning batareyangiz voltaji 30 voltdan oshadi deb taxmin qilingan,

"Maks tarixi: kichkina ajdaho" videojuego: 10 qadam

"Maks tarixi: kichkina ajdaho" videoroligi: "Max tarixi: kichkina ajdaho" video -rolikining asosiy mavzusi. puedes seguir este paso a paso:

Raspberry Pi yordamida DIY past kuchlanishli tashqi yoritish boshqariladi: 11 qadam (rasmlar bilan)

Raspberry Pi yordamida DIY past kuchlanishli tashqi yoritish boshqariladi: Nega? Tan olishim kerak, men, boshqalar kabi, narsalarning (yoki IoT) Internetning katta muxlisiman. Men hali ham barcha chiroqlarimni, asboblarimni, old eshiklarimni, garajlarimni ulashdan charchadim va ochiq Internetda yana nima borligini kim biladi. Ayniqsa, bunday hodisalar bilan

Pikaxaga asoslangan raqamli termometr Maks va Min: 13 qadam

Maks va Min bilan Pikaxaga asoslangan raqamli termometr: (Iltimos, xabar qoldiring, lekin o'ta tanqidiy bo'lmang, bu mening birinchi ko'rsatmam !!) Bu men termopravnikimiz uchun tashqi haroratni ko'rsatish uchun. U Picaxe chipiga asoslangan, chunki ular arzon va ulardan foydalanish oson. Agar bu … uchun bo'lsa