Mundarija:

- 1-qadam: PWM modulini yaratish- manba fayl

- 2-qadam: PWM modulini yaratish- Vivado-ni sozlash

- 3-qadam: PWM modulini yaratish- loyiha faylini yaratish

- 4-qadam: PWM modulini yaratish- blokirovka qilish va fayllarni sozlash (I)

- 5-qadam: PWM modulini yaratish- bloklarni loyihalash va fayllarni sozlash (II)

- 6-qadam: PWM modulini yaratish- blokirovka qilish va fayllarni sozlash (III)

- 7-qadam: PWM modulini yaratish- bloklarni loyihalash va fayllarni sozlash (IV)

- 8-qadam: PWM modulini yaratish- blokirovka qilish va fayllarni sozlash (V)

- 9-qadam: PWM modulini yaratish- uskunani o'rnatish

- 10-qadam: PWM modulini yaratish- Bitstream yaratish va SDK-ni ishga tushirish

- 11-qadam: PWM modulini yaratish- Xilinx SDK-da yangi dastur yaratish

- 12-qadam: PWM modulini yaratish- Project Explorer-ga umumiy nuqtai nazar (I)

- 13-qadam: PWM modulini yaratish- Project Explorer-ga umumiy nuqtai nazar (II)

- 14-qadam: PWM modulini yaratish- Project Explorer-ga umumiy nuqtai nazar (III)

- 15-qadam: PWM modulini yaratish- PWM funktsiyasini yig'ish (I)

- 16-qadam: PWM modulini yaratish- PWM funktsiyasini yig'ish (II)

- 17-qadam: PWM modulini yaratish- PWM funktsiyasini yig'ish (III)

- 18-qadam: PWM modulini yaratish- uni ishga tushiring

- 19 -qadam: OV7670 bilan Digilent ZYBO -da video ishlov berish

- 20 -qadam: To'liq blok diagrammasi

- 21 -qadam: OV7670 -ni ZYBO -ga ulang

- 22 -qadam: Blok dizaynini yarating

- 23 -qadam: OV7670 kamerasini boshqarish va yozib olish uchun VHDL fayllarini qo'shing

- 24 -qadam: Cheklovlar faylini qo'shing

- 25 -qadam: HLS IP uchun IP Repo -ni qo'shing

- 26 -qadam: Modul va IP -ni qo'shing

- 27 -qadam: IP -ni sozlash sozlamalari

- 28 -qadam: PS IP -blokini qo'shing va sozlang

- 29 -qadam: 1 -qism. Servo dvigatellar uchun PWM modulini yaratish

- 30 -qadam: Video kirish tomonidagi ulanishlar (ajratilgan)

- 31 -qadam: OV7670 ga ulanish

- 32 -qadam: Videoning tashqi tomonidagi ulanishlar

- 33 -qadam: Blok va ulanishni avtomatlashtirishni ishga tushiring

- 34 -qadam: HDL o'rash moslamasini yarating

- 35 -qadam: Bitstream yaratish, uskunani SDK -ga eksport qilish, Vivadodan SDK -ni ishga tushirish

- 36 -qadam: SDK (FreeRTOS yo'q)

- 37 -qadam: FreeRTOS -ni amalga oshirish

- 38 -qadam: Foydalanish bo'yicha ko'rsatmalar

- 39 -qadam: Manbalar va havolalar

- Muallif John Day day@howwhatproduce.com.

- Public 2024-01-30 13:28.

- Oxirgi o'zgartirilgan 2025-01-23 15:14.

2-o'qli servo PWM boshqaruvini yaratish haqida batafsil ma'lumot olish uchun birinchi bosqichdan boshlang.

To'liq loyiha uchun katta blok -sxemadan boshlang (19 -qadam).

Biz ishlatgan kamera + Pan/tilt sozlash:

Servolarni ulash uchun Digilent -dan PmodCON3 ishlatilgan.

1-qadam: PWM modulini yaratish- manba fayl

2-qadam: PWM modulini yaratish- Vivado-ni sozlash

Birinchidan, Xilinx veb -saytidan Vivado Design Suite -ni yuklab oling. Barcha dizayn to'plamini, shu jumladan Vivado Software Development Kit (SDK) ni o'rnating. Ushbu loyiha 2017.2 versiyasidan foydalanadi.

Shu bilan birga, Digilent Adept 2 Zybo karta drayveri sifatida ham o'rnatilishi kerak.

3-qadam: PWM modulini yaratish- loyiha faylini yaratish

Loyiha faylini yaratishdan oldin, Zybo faylini bu erda qo'llanma sifatida to'g'ri o'rnatilganligiga ishonch hosil qilishingiz kerak:

Vivado versiyasi 2015.1 va undan keyingi kartalarga fayllarni o'rnatish

Vivado 2017.2 -ni oching. "Tez ishga tushirish" da "Loyiha yaratish" -"Keyingi" -"Loyiha nomi" (Loyihangiz nomini shu erga ayting) -> "Loyiha turi" ni bosing. Loyiha turida RTL loyihasini tanlang va "Hozir manbalarni ko'rsatmang" belgisini qo'ying. Keyin, standart qism uchun "taxtalar" va "zybo" ni ko'rsatiladigan nom sifatida tanlang. Keyin, loyihani boshlash uchun Finish tugmasini bosing.

4-qadam: PWM modulini yaratish- blokirovka qilish va fayllarni sozlash (I)

Flow Navigator -da "" Blok dizaynini yaratish "-ni bosing va OK tugmasini bosing. kerakli IP -ni qo'shish uchun "+" belgisini bosing. Qo'shish:

- Bitta ZYNQ7 protsessor tizimi ikkita AXI taymer

- Ikkita AXI taymer

5-qadam: PWM modulini yaratish- bloklarni loyihalash va fayllarni sozlash (II)

IP -ni qo'shgandan so'ng, blokirovkani avtomatlashtirish va ulanishni avtomatlashtirishni ishga tushiring. Avtomatlashtirish tugagandan so'ng, "axi_timer_0" blokida pwm0 -> Tashqi qilish -ni o'ng tugmasini bosing. Pwm0 tashqi pinini pwm_Xaxis deb nomlang. Shuningdek, yuqoridagi jarayonni "axi_timer_1" blokida takrorlang va pwm0 tashqi pinini pwm_Zaxis deb nomlang.

6-qadam: PWM modulini yaratish- blokirovka qilish va fayllarni sozlash (III)

E'tibor bering, har safar Vivadoda blok dizaynini tugatganimizda, biz HDL o'rash moslamasini yaratishimiz kerak. Chunki bu har bir loyiha uchun yuqori darajali modul bo'ladi.

7-qadam: PWM modulini yaratish- bloklarni loyihalash va fayllarni sozlash (IV)

Endi biz blok -sxemamizga ulangan pinlarni belgilash uchun cheklov faylini o'rnatishimiz kerak. "Bloklar dizayni" oynasini yoping, "Manbalar to'g'risida" yorlig'idagi "Manbalarni qo'shish"-> Cheklovlarni qo'shing yoki yarating-> Zybo-Master.xdc-ni bizning cheklovchi fayllarimiz sifatida qo'shing.

8-qadam: PWM modulini yaratish- blokirovka qilish va fayllarni sozlash (V)

Cheklovlar papkasidan Zybo-Master.xdc cheklovchi faylini oching, biz chiqish signallari sifatida belgilamoqchi bo'lgan portlarni izohdan chiqaring va "get_ports {XXXX}" nomini o'zgartiring, bu XXXX blok diagrammada ko'rsatilgan tashqi pinni bildiradi. Cheklov faylining sozlanishi rasmda ko'rsatilgan.

9-qadam: PWM modulini yaratish- uskunani o'rnatish

Servo motorlarni Pmod CON3 ga ulang. TowerPro SG90 - biz ushbu loyihada ishlatgan servo dvigatel modeli. Servo dvigatel simlari uchun to'q sariq rangli sim Pmod CON3 dagi SIG piniga ulangan PWM signalini ifodalaydi. Qizil sim Vcc - bu Pmod CON3 dagi VS piniga ulangan quvvat simidir. Nihoyat, jigarrang sim Gnd - GND piniga ulangan tuproqli sim. Keyin, Pmod CON3 ni Zybo platasidagi JD portining yuqori qatoriga joylashtiring.

10-qadam: PWM modulini yaratish- Bitstream yaratish va SDK-ni ishga tushirish

1. Project Navigator ilovasida BitStream yaratish -ni ishga tushiring.

2. Uskuna eksporti: Fayl> Eksport> Uskuna eksporti-> "bit oqimini o'z ichiga oladi" belgisini qo'ying-> OK 3. SDK-ni ishga tushiring: Fayl-> SDK-ni ishga tushiring.

11-qadam: PWM modulini yaratish- Xilinx SDK-da yangi dastur yaratish

Yangi ilova yarating:

Fayl> Yangi> Dastur loyihasi -> Loyihangiz nomini kiriting -> Finish

Project Explorer ostida uchta papka bo'lishi kerak.

Bunday holda, "design_1_wrapper_hw_platform_0" - bu Vivado tomonidan ilgari eksport qilingan papka. Axis_2_PWM_SDK_bsp - bu kartani qo'llab -quvvatlash to'plami papkasi. Va Axis_2_PWM_SDK - bu SDK -dagi asosiy loyiha papkamiz. Axis_2_PWM_SDK "src" papkasida "helloworld.c" faylini ko'rishingiz mumkin, bu erda asosiy fayl "helloworld.c" dir.

12-qadam: PWM modulini yaratish- Project Explorer-ga umumiy nuqtai nazar (I)

Project Explorer ostida ba'zi fayllarni tekshirib ko'ramiz. Birinchidan, "design_1_wrapper_hw_platform_0" papkasida "system.hdf" ni oching. Bu fayl ps7_cortex9 protsessorining manzil xaritasini va bizning dizaynimizda mavjud bo'lgan IP -bloklarni ko'rsatadi.

13-qadam: PWM modulini yaratish- Project Explorer-ga umumiy nuqtai nazar (II)

Keyin "Axis_2_PWM_SDK_bsp" jildidagi "qo'shish" va "libsrc" faylini tekshiring. Bu erdagi kutubxona fayllari bizga qo'shimcha qurilmalar bilan registrlarni "o'ynatmasdan" ishlash imkonini beradi.

14-qadam: PWM modulini yaratish- Project Explorer-ga umumiy nuqtai nazar (III)

BSP hujjatlari orqali xtmrctr.h AXI Taymer bilan bog'liq Xilinx taymerini boshqarish kutubxonasi sifatida topiladi. Odatda, biz bu erda kerakli PWM funktsiyasini topa olamiz. Ammo, agar siz "tmrctr_v4_3" hujjatlarini o'qib chiqsangiz, bu haydovchi hozirda qurilmaning PWM ishlashini qo'llab -quvvatlamasligini ko'rsatadi. PWM funktsiyasining etishmasligi tufayli, biz xtmrctr.h va AXI Timer v2.0 LogiCORE IP Mahsulot qo'llanmasi yordamida PWM funktsiyasini yakunlashimiz kerak.

15-qadam: PWM modulini yaratish- PWM funktsiyasini yig'ish (I)

"Helloworld.c" asosiy fayliga qaytsak, quyidagi sarlavha fayllarini o'z ichiga oladi:

16-qadam: PWM modulini yaratish- PWM funktsiyasini yig'ish (II)

"Xparameters.h" orqali ikkita AXI TImerning asosiy manzillarini aniqlang.

17-qadam: PWM modulini yaratish- PWM funktsiyasini yig'ish (III)

Kerakli PWM funktsiyasini yarating.

Duty_val: daraja qiymatini ish tsikliga aylantiradi. Soat davri ham belgilanishi kerak.

PWM_START: PWM registr manzilini belgilang va PWM ishlab chiqarishni boshlang.

PWM_STOP: PWM registr manzilini tayinlash va PWM ishlab chiqarishni to'xtatish.

Qolgan demo kodlar "Axlow_2_PWM_SDK" ostida "helloworld.c" da ko'rsatilgan.

18-qadam: PWM modulini yaratish- uni ishga tushiring

1. SDK orqali FPGA dasturlash

- USB port orqali Zybo Board -ni kompyuterga ulang.

- Xilinx asboblari -> FPGA dasturi

2. Dasturni ishga tushiring

"Ishga tushirish" belgisini bosing va menyuni oching -> Boshqa ishga tushirish -> Uskuna ustida ishga tushirish

3. SDK terminali

- SDK terminalini oching -Seriya portiga ulanish -> OK

- Dasturni ishga tushiring. Agar demo -kod muvaffaqiyatli ishlasa, "Initializatsiya bajarildi!" SDK terminalida.

19 -qadam: OV7670 bilan Digilent ZYBO -da video ishlov berish

To'liq arxiv fayli biriktirilgan.

20 -qadam: To'liq blok diagrammasi

Bu loyihadagi barcha ulanishlar va IP -bloklarning to'liq diagrammasini ko'rsatadi

21 -qadam: OV7670 -ni ZYBO -ga ulang

Ov7670 modulini ZYBO Pmods -ga ulash uchun ulanish yarating

Ma'lumotlar Pmod - bu Pmod D

Pmod boshqaruv Pmod C

Bundan tashqari, ushbu qo'llanmaning birinchi yarmida ko'rsatilgan PmodCON3 va servolarni ulang

22 -qadam: Blok dizaynini yarating

Flow Navigator -da "Blok dizaynini yaratish" tugmachasini bosing va OK tugmasini bosing.

23 -qadam: OV7670 kamerasini boshqarish va yozib olish uchun VHDL fayllarini qo'shing

Ushbu bosqichga biriktirilgan VHDL fayllarini loyihaga qo'shing

24 -qadam: Cheklovlar faylini qo'shing

Loyihangizga biriktirilgan cheklovlar faylini qo'shing.

25 -qadam: HLS IP uchun IP Repo -ni qo'shing

Zip faylini biriktiring va "HLS_repo" deb nomlangan yangi katalogda (papkada) xuddi shunday nomlangan yangi papkaga oching.

IP-katalogiga o'ting va "Ma'bad qo'shish …" -ni o'ng tugmasini bosib, loyihangizga IP-omborini qo'shing.

"HLS_repo" katalogiga o'ting va uni tanlang.

Majburiy emas: o'zingiz uchun HLS video ishlov berish blokini yarating!

26 -qadam: Modul va IP -ni qo'shing

Ov7670_axi_stream_capture, debounce va ov7670_controller modullarini blok -sxemaga fonni o'ng tugmasini bosib, "Modul qo'shish …" ni tanlab qo'shing.

Xuddi shunday, IP -ni qo'shing:

- HLS_Video_Track

- Video ramka buferi yozish

- Video ramka buferini o'qish

- Video vaqtni boshqarish moslamasi

- AXI4-video oqimiga oqim

- "Dilim" ning 3 -qismi

- Doimiy

- AXI taymerining 2 qismi

27 -qadam: IP -ni sozlash sozlamalari

Rasmlarda ko'rsatilgandek

28 -qadam: PS IP -blokini qo'shing va sozlang

ZYNQ7 protsessing tizimini blok -sxemaga qo'shing

konfiguratsiyani tahrirlash:

-

PS-PL konfiguratsiyasi

-

HP

- S HP 0 ni yoqing

- S HP 1 -ni yoqing

-

-

Soat konfiguratsiyasi

-

PL mato soatlari

- FCLK_0 100 MGts da

- FCLK_1 25 MGts da (OutputClock)

- FLCK_2 35 MGts da (<= 50 MGts) (CameraClock)

-

29 -qadam: 1 -qism. Servo dvigatellar uchun PWM modulini yaratish

Axi_timer_0 pwm0 ni yangi pwm_Xaxis chiqish portiga olib keling

Axi_timer_1 pwm0 ni yangi pwm_Zaxis chiqish portiga olib keling

30 -qadam: Video kirish tomonidagi ulanishlar (ajratilgan)

Video kirish tomonidagi IP -bloklarni to'g'ri ulang

(* bu ulanishlar avtomatlashtirish paytida to'g'ri variantlarni tanlash orqali yaratilishi kerak) axi_stream_capture -dan "aclk":

- ap_clk video ramka buferida yozish

- ap_clk HLS video oqimini qayta ishlash blokida

- *Video ramka buferidan AXI smartconnect IP -dagi aclk S_AXI_HP0 ga yozing.

- *HLS video ishlov berish blokining S_AXI kanallari uchun AXI Interconnect IP kanallariga mos keladigan aclk va video ramka buferi PS blokiga S_AXI_HP0_ACLK yozadi.

Video oqimi signali oddiygina ketma -ket tortishish blokidan Zynq xotira interfeysiga ulanadi.

- Video ta'qib qilish blokidan HLS ishlov berish blokiga o'tadi.

- HLS blokidan qayta ishlangan video ramka buferi yozish blokiga o'tadi.

- *Ramka buferi yozish bloki Zynq PS blokidagi HP0 interfeysiga ulanadi.

- Qo'lga tushirish blokining chiqishidan m_axis_tuser signali HLS ishlov berish blokidagi video_in_TUSER kirish signaliga ham, o'sha blokdagi ap_start signaliga ham qo'lda ulanadi.

TUSER (tuser) signali AXI video oqimi protokoli tomonidan videoning ramkasi boshlanishini bildirish uchun ishlatiladi. Avtobusning bitta signalini ulaganda va uni shu tarzda ajratganda, uni avtobusning qolgan to'xtash joyiga ulash lozim. Vivado, agar siz signalni qo'lda ulasangiz, u odatda ulanadigan narsani uzib tashlamoqchi ekanligingizni taxmin qiladi.

IP -bloklarni sozlash:

Video ramka buferiga yozing:

Video formatlari: RGB8

Maksimal ustunlar: 1280 (> = 640) Maksimal qatorlar: 960 (> = 480) Maksimal ma'lumotlar kengligi: 8

31 -qadam: OV7670 ga ulanish

Ov7670_axi_stream_capture blokida

- Barcha kirishni tashqi qilib qo'ying (pinni sichqonchaning o'ng tugmasi bilan bosing va menyudan tanlang yoki chap tugmani bosing-> ctrl+T).

- Ismlarni shunday qoldiring

Ov7670_controller blokida

- Blokning barcha chiqishini tashqi qilib qo'ying

- Config_finished portini led0 deb o'zgartiring

- clk -ni CameraClock -ga ulang (<= 50MHz) (FCLK_2)

O'chirish blokida

- button1 kirishini btn0 deb nomlangan tashqi kirish portiga ulang

- out1 -ni ov7670_controller IP -blokidagi qayta yuborish liniyasiga ulang

- tugma2 kirishini btn3 deb nomlangan tashqi kirish portiga ulang

- video tortishish soati uchun protsessor tizimining Reset IP -dagi ext2reset_in kirishiga out2n -ni ulang. (*IP yaratilgandan keyin buni qilish kerak bo'lishi mumkin))

- clk -ni CameraClock -ga ulang (<= 50MHz) (FCLK_2)

32 -qadam: Videoning tashqi tomonidagi ulanishlar

Video vaqtni boshqarish moslamasi (VTC), AXI4-Stream to Video Out va tilim bloklari uchun ulanishlar

- Vid_io_out_clk va VTC clk uchun 25 MGts soat (FCLK_1) dan foydalaning

- AXI4-Stream to Video Out-da ochish uchun 100 MGts soat (FCLK_0) dan foydalaning

- vtiming_out dan vtiming_in

- Video ramka buferini o'qish m_axis_video AXI4-Stream-dan Video Out video_in-ga o'tadi.

- vtg_ce gen_clken -ga o'tadi

- VTC clken, aclken, vid_io_out_ce ni Dout doutga bog'lang [0: 0]

- Vid_hsync va vid_vsync -ni mos ravishda vga_hs va vga_vs tashqi chiqish portlariga olib keling. (rasmda yo'q)

Dilim:

-

Dilimlarni biriktirilgan rasmlarda ko'rsatilgandek sozlash kerak

- bloklarni slice_red, slice_green va slice_blue deb o'zgartiring

- blok nomlari bo'yicha rasmlarda ko'rsatilgandek bo'lak oralig'ini sozlash

- har bir bo'lakni rasmda ko'rsatilgandek tashqi port chiqishiga ulang.

- vid_data [23: 0] har bir bo'lak uchun kirishga ulanadi (Din [23: 0])

33 -qadam: Blok va ulanishni avtomatlashtirishni ishga tushiring

ZYNQ7 PS blokidagi narsalarni ulash uchun Blok avtomatizatsiyasini ishga tushiring. Rasmda ko'rsatilgandek.

Barcha ulanish IP -larini yaratish uchun ulanish avtomatizatsiyasini ishga tushiring. Har bir rasmdagi barcha variantlarga katta e'tibor bering.

O'chirish blokida, video tortishish soati domeniga out2n -ni ulang, protsessor tizimi Reset ext_reset_in kirishiga.

34 -qadam: HDL o'rash moslamasini yarating

Blok dizayni uchun HDL o'rash moslamasini yarating.

Uni yuqori modul sifatida o'rnating.

35 -qadam: Bitstream yaratish, uskunani SDK -ga eksport qilish, Vivadodan SDK -ni ishga tushirish

Eksportga bit oqimini kiritganingizga ishonch hosil qiling.

Bitstream yaratish juda uzoq vaqt talab qilishi mumkin.

Keyin SDK -ni ishga tushiring

36 -qadam: SDK (FreeRTOS yo'q)

Ushbu versiya FreeRTOS -ni ishlatmasdan hamma narsani qiladi, kodni yaxshi kondensatlaydi.

Uskuna dizayni asosida mustaqil BSP yarating. Standart variantlar yaxshi bo'lishi kerak. BSP manbalari yaratilganligiga ishonch hosil qiling.

Rasmda ko'rsatilgandek ilova yarating. (bo'sh ariza)

Avtomatik yaratilgan asosiy faylni o'chiring va biriktirilgan fayllarni import qiling.

37 -qadam: FreeRTOS -ni amalga oshirish

Bu versiya FreeRTOS -dan foydalanadi. Uskuna dizayniga asoslangan FreeRTOS901 BSP -ni yarating. Standart variantlar yaxshi bo'lishi kerak. BSP manbalari yaratilganligiga ishonch hosil qiling.

Rasmda ko'rsatilgandek ilova yarating. (bo'sh ariza)

Avtomatik yaratilgan asosiy faylni o'chiring va biriktirilgan fayllarni import qiling.

38 -qadam: Foydalanish bo'yicha ko'rsatmalar

Bu loyihani ishga tushirish biroz qiyin. Bosqichlarni tartibda bajaring.

ZYBO yoqilganda hech narsa yuklamasligiga ishonch hosil qiling. Bu shuni anglatadiki, Bajarilgan LED yonmasligi kerak. Buning bir usuli - yuklash manbai o'tish moslamasini JTAG -ga o'rnatish.

SDK -dan dastur qilmoqchi bo'lgan loyihani (FreeRTOS yoki yo'q) oching

- ZYBO -ni yoqing. Bajarilgan LED yonmasligi kerak.

- FPGA -ni bitli fayl bilan dasturlash. Bajarilgan LED yonishi kerak. Led0 yonmasligi kerak.

- Kodni ishga tushiring (agar shunday qilsangiz, boshlang'ich to'xtash nuqtasidan o'tishni unutmang).

Bu vaqtda siz VGA displeyingizda chiqishni olishingiz kerak.

Qayta ishga tushirish uchun (agar u xato bo'lsa yoki boshqa bo'lsa): PS-SRST tugmachasini tezda bosing yoki ZYBO-ni o'chiring va keyin qayta yoqing. 2 -bosqichdan davom eting.

Nosozliklarni tuzatuvchi yordamida protsessorni to'xtatib qo'yish kameraning harakatlanish o'rniga o'rnini ushlab turishiga olib keladi. Video oqimi baribir davom etadi.

39 -qadam: Manbalar va havolalar

Xilinx ma'lumotnomalari va hujjatlari:

- PG044 - video chiqish uchun AXI -oqim

- PG278 - Video ramka buferi o'qish/yozish

Boshqa havolalar:

- Lauri blogi - VDMA usuli

- Lauri blogi - OV7670 - BRAM yordamida VGA chiqishi

- Hamsterworks wiki, Mayk Fields, OV7670 kodining asl manbasi

- Vaqt jadvalining asosiy ko'rsatkichlari ko'rsatilgan ma'lumotlar jadvali

Tavsiya:

Televizorni va ulangan Raspberry Pi -ni bir xil masofadan boshqarish pulti bilan boshqarish: 4 qadam

Xuddi shu masofadan boshqarish pulti yordamida televizor va Raspberry Pi -ni boshqarish: Raspberry Pi -ni infraqizil masofadan boshqarish pulti bilan boshqarish uchun biz ilgari LIRC -dan foydalana olardik. Bu 4.19.X yadrosiga qadar ishlagan, LIRC -ni ishga olish ancha qiyin bo'lgan. Ushbu loyihada bizda Raspberry Pi 3 B+ televizorga ulangan va biz

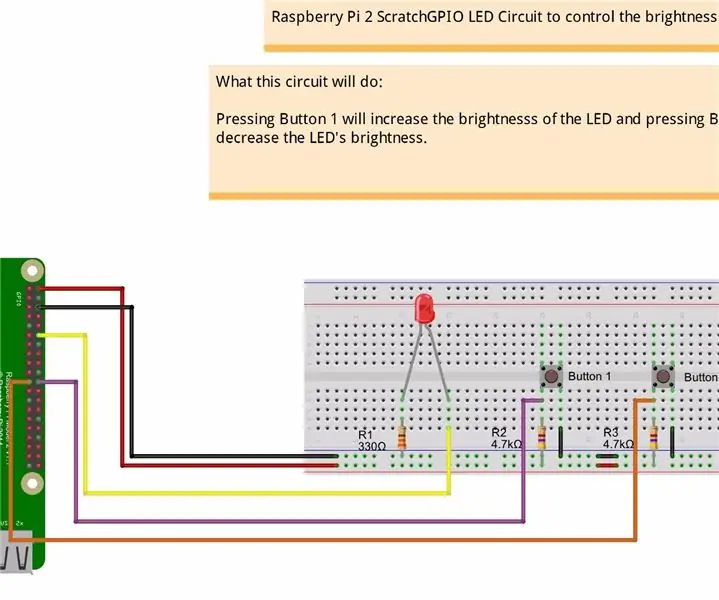

Yorqinlikni boshqarish PWM asosidagi LEDni boshqarish tugmachalari, Raspberry Pi va skretch yordamida: 8 qadam (rasmlar bilan)

Yorqinlikni boshqarish PWM asosidagi LEDni boshqarish tugmachalari, Raspberry Pi va Scratch yordamida: Men PWMning o'quvchilarimga qanday ishlashini tushuntirishga harakat qilardim, shuning uchun men o'z oldimga ikkita tugma yordamida LEDning yorqinligini boshqarishga harakat qildim. - bitta tugmachaning yorqinligini oshiradi, ikkinchisi esa uni o'chiradi. Dastur uchun

3D printerni issiqlik muhofazasi: 3D bosib chiqarishdagi burilishni tuzatish: 4 qadam

3D -printerning issiqlik muhofazasi: 3D -printerda burilishni to'g'rilash: 3D -printerga ega bo'lgan har bir kishi bu yoki boshqa nuqtada burilish muammosiga duch kelgan. Bir necha soat davom etadigan bosmalar yo'q qilinadi, chunki taglik to'shakdan chiqib ketgan. Bu muammo asabiylashishi va ko'p vaqt talab qilishi mumkin. Xo'sh, qanday ahmoqlik

Taymer funktsiyasi bilan televizorni masofadan boshqarish pulti yordamida uy jihozlarini qanday boshqarish mumkin: 7 qadam (rasmlar bilan)

Uy asbob -uskunalarini masofadan boshqarish pulti bilan taymer funktsiyasi yordamida qanday boshqarish mumkin: Iste'mol bozoriga 25 yil kirganidan keyin ham, infraqizil aloqa so'nggi kunlarda juda dolzarb bo'lib qolmoqda. Bu sizning 55 dyuymli 4K televizoringiz yoki avtomobilingizning ovoz tizimidan qat'i nazar, hamma narsaga javob berish uchun IQ masofadan boshqarish pulti kerak

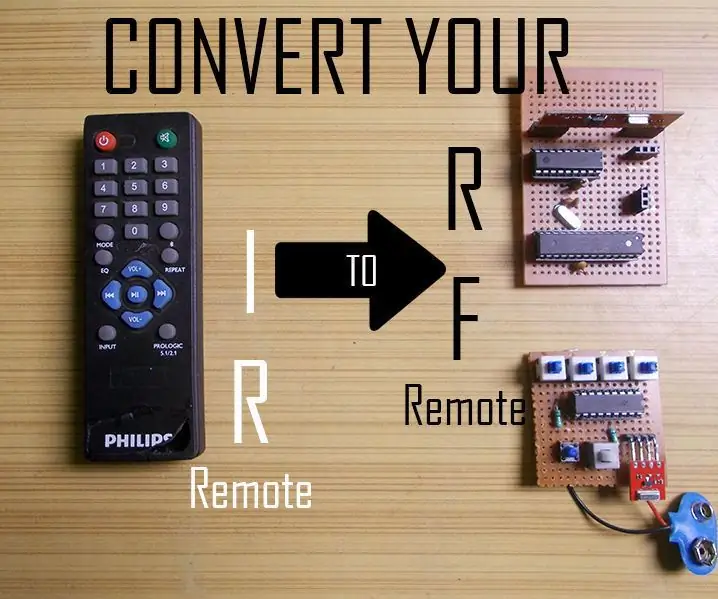

IR masofadan boshqarish pultini masofadan boshqarish pultiga aylantirish: 9 qadam (rasmlar bilan)

IR masofadan boshqarish pultini masofadan boshqarish pultiga aylantiring: "Bugungi yo'riqnomada" sizga qanday qilib umumiy chastotali modulni mikrokontroldorisiz ishlatishingiz mumkinligini ko'rsataman, bu esa oxir -oqibat bizni har qanday qurilmaning IR masofadan boshqarish pultini RFga aylantirishga imkon beradi. Masofadan boshqarish pulti. Konvertatsiya qilishning asosiy afzalligi