Mundarija:

- Muallif John Day day@howwhatproduce.com.

- Public 2024-01-30 13:25.

- Oxirgi o'zgartirilgan 2025-01-23 15:14.

Men buni ko'rsatma sifatida yozyapman, chunki VHDL -ga ma'lumot olish va kesh tekshirgichini loyihalashni boshlash biroz qiyin bo'lgan. Shunday qilib, men o'zimni noldan kesh tekshirgichini yaratdim va uni FPGA -da muvaffaqiyatli sinab ko'rdim. Men bu erda oddiy to'g'ridan-to'g'ri xaritali kesh tekshirgichini, shuningdek, kesh tekshirgichini sinab ko'rish uchun butun protsessor-xotira tizimini modellashtirdim. Umid qilamanki, siz ushbu ko'rsatmalarni o'zingizning kesh tekshirgichlaringizni loyihalashtirish uchun foydali deb bilasiz.

1 -qadam: Xususiyatlar

Bu biz loyihalashtirmoqchi bo'lgan kesh tekshirgichining asosiy xususiyatlari:

- To'g'ridan -to'g'ri xaritalar. (assotsiativ xaritali kesh boshqaruvchisini qidirsangiz, bu havolaga o'ting)

- Yagona bankli, blokirovka qiluvchi kesh.

- Yozish xitlarini yozish siyosati.

- Yozishni o'tkazib yubormaslik siyosati ajratiladi yoki yoziladi.

- Yozish buferi yoki boshqa optimallashtirish yo'q.

- Tag Array kiritilgan.

Bundan tashqari, biz kesh xotira va asosiy xotira tizimini yaratamiz.

Kesh xotirasining standart (sozlanishi) xususiyatlari:

- 256 baytli bitta bankli kesh.

- 16 keshli satr, har bir kesh chizig'i (blok) = 16 bayt.

Asosiy xotira texnik xususiyatlari:

- Sinxron o'qish/yozish xotirasi.

- Ko'p bankli Interleaved xotira - to'rtta xotira banki.

- Har bir bank hajmi = 1 kB. Shunday qilib, umumiy hajmi = 4 kB.

- 10 bitli manzil shinasi bilan Word (4 bayt) manzilli xotira.

- O'qish uchun yuqori tarmoqli kengligi. Ma'lumotlar kengligi = 16 baytni bitta soat aylanishida o'qing.

- Ma'lumotlar kengligi = 4 bayt.

QAYD: agar siz 4 tomonlama assotsiativ kesh tekshiruvi dizaynini qidirsangiz, mening yangi ko'rsatmalarni tekshiring

2 -qadam: Butun tizimning RTL ko'rinishi

Yuqori modulning to'liq RTL ko'rinishi rasmda ko'rsatilgan (protsessordan tashqari). Avtobuslar uchun standart ko'rsatkichlar:

- Barcha ma'lumotlar avtobuslari 32 bitli avtobuslar.

- Manzil avtobusi = 32 bitli avtobus (lekin bu erda faqat 10 bitli xotira mavjud).

- Ma'lumotlar bloki = 128 bit (o'qish uchun keng tarmoqli kengligi).

- Barcha komponentlar bir xil soat bilan boshqariladi.

3 -qadam: Sinov muhiti

Yuqori modul oddiy sinov o'tkazgich yordamida sinovdan o'tkazildi, u oddiy quvurli bo'lmagan protsessorni modellashtiradi (chunki butun protsessorni loyihalash oson emas!). Sinov dastgohi xotiraga tez -tez ma'lumotlarni o'qish/yozish so'rovlarini beradi. Bu protsessor tomonidan bajariladigan barcha dasturlarda uchraydigan odatdagi "Yuklash" va "Do'kon" ko'rsatmalarini masxara qiladi. Sinov natijalari keshni boshqarish moslamasini muvaffaqiyatli tekshirdi. Quyida kuzatilgan test statistikasi keltirilgan:

- O'qish/yozish bo'yicha barcha Miss va Xit signallari to'g'ri yaratilgan.

- Ma'lumotlarni o'qish/yozish bo'yicha barcha operatsiyalar muvaffaqiyatli o'tdi.

- Ma'lumotlarning nomuvofiqligi/nomuvofiqlik muammolari aniqlanmadi.

- Dizayn Maxm uchun muvaffaqiyatli tasdiqlandi. Ish chastotasining chastotasi = 110 MGts Xilinx Virtex-4 ML-403 platasida (butun tizim), 195 MGts faqat kesh tekshiruvi uchun.

- Asosiy xotira uchun blokli RAMlar taxmin qilingan. Boshqa barcha massivlar LUT -larda amalga oshirildi.

4 -qadam: biriktirilgan fayllar

Bu blogga quyidagi fayllar biriktirilgan:

- . VHD fayllari kesh tekshirgichi, ma'lumotlar keshi, asosiy xotira tizimi.

- Sinov dastgohi.

- Hujjatlar kesh tekshiruvi.

Eslatmalar:

- Bu erda taqdim etilgan kesh tekshirgichining texnik xususiyatlarini to'liq tushunish uchun hujjatlarni ko'rib chiqing.

- Koddagi har qanday o'zgarishlar boshqa modullarga bog'liq. Shunday qilib, o'zgarishlar oqilona bo'lishi kerak. Men bergan barcha sharhlar va sarlavhalarga e'tibor bering.

- Agar biron sababga ko'ra, Operativ xotira bloklari asosiy xotira uchun hisoblanmasa, xotira hajmini kamaytiring, so'ngra fayllar bo'yicha manzil shinalari kengligi o'zgaradi va hokazo. Shunday qilib, xuddi shu xotira LUT yoki tarqatilgan RAMda amalga oshirilishi mumkin. Bu yo'nalish vaqtini va resurslarini tejaydi. Yoki maxsus FPGA hujjatlariga o'ting va RAMni blokirovka qilish uchun mos keladigan kodni toping va shunga mos ravishda kodni tahrir qiling va bir xil manzillar shinasi kengligi spetsifikatsiyalaridan foydalaning. Altera FPGA -lar uchun ham xuddi shunday usul.

Tavsiya:

Simsiz Xbox 360 tekshirgichining qobig'ini almashtirish: 15 qadam (rasmlar bilan)

Simsiz Xbox 360 tekshirgichining qobig'ini almashtirish: Xbox 360 tekshirgichining qobig'ini yangi qobiqqa almashtirish bo'yicha bosqichma -bosqich ko'rsatma. Bu o'quv qo'llanma o'quvchilarga video o'yin orqali apparat, elektrotexnika/kompyuter injiniringi va informatika tamoyillari haqida asosiy tushunchalarga ega bo'lishga yordam berish uchun ishlatilishi mumkin

VHDL-da to'rt tomonlama oddiy assotsiativ kesh tekshirgichining dizayni: 4 qadam

VHDL-da to'rt tomonlama oddiy assotsiativ kesh boshqaruvchisining dizayni: oldingi ko'rsatmamizda biz to'g'ridan-to'g'ri xaritali keshni boshqaruvchi dizaynini ko'rdik. Bu safar biz bir qadam oldinga siljiymiz. Biz oddiy to'rt tomonlama assotsiativ kesh tekshirgichini loyihalashtiramiz. Afzallikmi? Kamroq o'tkazib yuborish darajasi, lekin narxiga

VHDL va Verilog -dagi oddiy VGA boshqaruvchisi dizayni: 5 qadam

VHDL va Verilog -dagi oddiy VGA boshqaruvchisini loyihalash: Bu ko'rsatmada biz RTL -da oddiy VGA boshqaruvchisini loyihalashtirmoqchimiz. VGA Controller - bu VGA displeylarini boshqarishga mo'ljallangan raqamli elektron. U Frame Buffer -dan (VGA Xotirasi) o'qiladi, u ko'rsatiladigan ramkani ifodalaydi va kerak bo'ladi

PCB dizayni oddiy va oson qadamlar bilan: 30 qadam (rasmlar bilan)

PCB dizayni oddiy va oson qadamlar bilan: SALOM DO'STLAR PCB dizaynini o'rganmoqchi bo'lganlar uchun juda foydali va oson qo'llanma boshlanadi

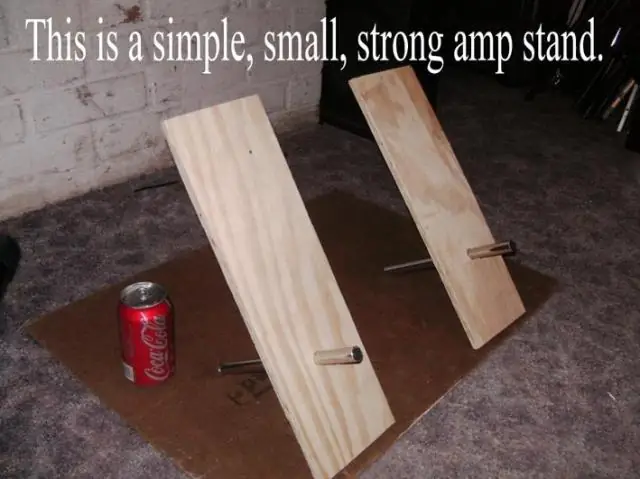

Gitara kuchaytirgichli stend - "Afrika stullari" dizayni - oddiy, kichik, kuchli, oson, bepul yoki haqiqiy arzon: 9 qadam

Gitara Amp Tilt Stend - "Afrika stul" dizayni - Oddiy, Kichik, Kuchli, Oson, Bepul yoki Haqiqiy Arzon: Gitara Amp Tilt Stend - Juda oson - oddiy, kichik, kuchli, bepul yoki haqiqiy arzon. Barcha o'lchamdagi amperlar uchun, hatto alohida boshli katta shkaflar. Faqat kerakli o'lchamdagi taxtalar va quvurlarni tayyorlang va sizga kerak bo'lgan deyarli barcha uskunalar kerak bo'ladi