Mundarija:

- Muallif John Day day@howwhatproduce.com.

- Public 2024-01-30 13:25.

- Oxirgi o'zgartirilgan 2025-01-23 15:14.

Ushbu qo'llanmada biz RTL -da oddiy VGA boshqaruvini loyihalashtirmoqchimiz. VGA Controller - bu VGA displeylarini boshqarishga mo'ljallangan raqamli elektron. U ko'rsatiladigan ramkani ifodalovchi Frame Buffer (VGA Memory) dan o'qiydi va ko'rsatish uchun kerakli ma'lumotlarni va sinxronizatsiya signallarini ishlab chiqaradi.

Agar siz Verilog/System verilog kodini qidirmoqchi bo'lsangiz: Verilogdagi VGA Controller va Video System blogimga tashrif buyuring.

1 -qadam: VGA tekshirgichining interfeysi

Quyida VGA kontrolleridagi asosiy interfeys signallari keltirilgan

- Pikselli soat yoki VGA soati

- HSYNC va VSYNC signallari

Tanlangan VGA displeyi uchun avval uni haydash uchun zarur bo'lgan Pixel Clock chastotasini hisoblash kerak. Bu 3 parametrga bog'liq: umumiy gorizontal piksellar, umumiy vertikal piksellar, ekranni yangilash tezligi.

Odatda, F = THP * TVP * yangilanish tezligi

Har xil VGA displeylari uchun zarur bo'lgan pikselli soat hujjatlarini biriktirilgan RARda toping.

HSYNC va VSYNC signallari Pixel soatlaridan ishlab chiqariladi. HSYNC va VSYNC signallarining vaqti parametrlar soniga bog'liq: gorizontal va vertikal old chiziq, gorizontal va vertikal orqa chiziq, gorizontal va vertikal displey piksellari, gorizontal va vertikal sinxronlash pulslarining kengligi va qutblari.

Bu parametrlar tanlangan VGA displeyi uchun standartlashtirilgan. Bu hujjatlarni biriktirilgan RARda toping.

Bu parametrlar VGA Controller IP -da sozlanishi parametrlardir.

2 -qadam: VGA displeyi bilan VGA boshqaruvchisini birlashtirish

Rasmda VGA displeyini VGA displeyi bilan qanday birlashtirish mumkinligi ko'rsatilgan. Tizimni to'ldirish uchun sizga yana ikkita komponent kerak bo'ladi:

- Ramka buferi: ko'rsatiladigan ramkani saqlaydigan xotira.

- Video DAC: RGB raqamli ma'lumotlarini o'zgartiradigan va VGA displeyini RGB analog signallari bilan mos keladigan kuchlanish darajasida boshqaradigan DAC.

Oddiy va ommabop Video DAClardan biri bu ADV7125. Bu RGB raqamli so'zlarni 0-0.7 V analog signallarga aylantiradigan va VGA displeyini boshqaradigan 8 bitli DAC.

3 -qadam: ramka bufer dizayni

Bu ko'rsatiladigan tasvirni "saqlaydigan" xotira. Odatda bu RAM yoki ba'zida ROM. Biz tasvirni ko'rsatish uchun ramka buferini qanday loyihalashni muhokama qilamiz. Frame bufer bu raqamli ma'lumotni VGA Controller buyrug'i bo'yicha Video DACga uzatadi.

Birinchidan, biz kerakli piksel chuqurligini aniqlashimiz kerak. U tasvirning sifatini, piksellar rangining xilma -xilligini aniqlaydi. 8-bitli DAC uchun biz pikselning asosiy rang komponentlarini ko'rsatishimiz kerak: R, G va B har biri 8 bitda. Bu shuni anglatadiki, piksel 24 bitli.

Har bir piksel Frame Buffer xotira joylarida ketma -ket saqlanadi.

Tasavvur qilaylik, tasvir 800x600 piksel.

Shuning uchun Frame Buffer 800x600 = 480000 x 24 bitli xotiraga muhtoj

Xotiraning umumiy hajmi 800x600x24 = taxminan 1400 kB.

Agar qora va oq tasvir bo'lsa, 800x600x1 = 60 kB taxminan.

Blokli RAMlar, ehtimol, Xilinx FPGA -larda Frame Buferni ifodalash uchun ishlatilgan.

4 -qadam: Eslatmalar

- Tanlangan DACga qarab VGA tekshirgichida qo'shimcha signallar kerak. Men ADV7125 dan foydalanganman.

- VGA displeyini haydashdan oldin VSYNC va HSYNC-dagi flip-floplar orqali tsikl kechikishlarini qo'shing. Buning sababi DAC va xotira kechikishidir. Piksel signallari HSYNC va VSYNC bilan sinxronlashtirilishi kerak. Menimcha, bu 2 tsikl kechikish edi.

- Agar ramka o'lchamlari cheklanganligi sababli berilgan o'lchamdagi ramka buferi FPGA -da ishlab chiqilmasa, tasvirni ko'rsatish uchun kichikroq xotiradan foydalaning va kodni to'liq ramka chegarasi emas, balki mavjud xotira chegarasidagi manzilga o'tkazish uchun tahrir qiling. Bu butun ekran bo'ylab bir xil tasvirni qayta -qayta takrorlaydi. Yana bir usul - bu piksellar sonini o'lchash, bunda har bir piksel butun tasvirni to'liq ekranda, kamroq aniqlikda ko'rsatish uchun takrorlanadi. Buni koddagi manzillarni ko'paytirish mantig'ini o'zgartirish orqali amalga oshirish mumkin.

- IP barcha FPGA-larda to'liq ko'chiriladi va Virtex-4 FPGA-da 100 MGts gacha tasdiqlangan.

5 -qadam: biriktirilgan fayllar

RAR tarkibiga quyidagilar kiradi:

- VGA tekshirgich kodi

- PDF VGA standartlari.

Tavsiya:

Arduino asosidagi DIY o'yin boshqaruvchisi - Arduino PS2 o'yin boshqaruvchisi - DIY Arduino Gamepad bilan Tekken o'ynash: 7 qadam

Arduino asosidagi DIY o'yin boshqaruvchisi | Arduino PS2 o'yin boshqaruvchisi | DIY Arduino Gamepad bilan Tekken o'ynash: Salom bolalar, o'yin o'ynash har doim qiziqarli, lekin o'zingizning shaxsiy o'yiningiz bilan o'ynash yanada qiziqarli, shuning uchun biz ushbu qo'llanmada arduino pro micro yordamida o'yin boshqaruvchisi qilamiz

VHDL-da to'rt tomonlama oddiy assotsiativ kesh tekshirgichining dizayni: 4 qadam

VHDL-da to'rt tomonlama oddiy assotsiativ kesh boshqaruvchisining dizayni: oldingi ko'rsatmamizda biz to'g'ridan-to'g'ri xaritali keshni boshqaruvchi dizaynini ko'rdik. Bu safar biz bir qadam oldinga siljiymiz. Biz oddiy to'rt tomonlama assotsiativ kesh tekshirgichini loyihalashtiramiz. Afzallikmi? Kamroq o'tkazib yuborish darajasi, lekin narxiga

VHDL -da oddiy kesh tekshirgichining dizayni: 4 qadam

VHDL -dagi oddiy kesh boshqaruvchisining dizayni: Men buni ko'rsatma sifatida yozyapman, chunki VHDL -dan ma'lumot olish va keshni boshqarishni loyihalashni boshlash biroz qiyin bo'lgan. Shunday qilib, men o'zimni noldan kesh tekshirgichini yaratdim va uni FPGA -da muvaffaqiyatli sinab ko'rdim. Menda p bor

PCB dizayni oddiy va oson qadamlar bilan: 30 qadam (rasmlar bilan)

PCB dizayni oddiy va oson qadamlar bilan: SALOM DO'STLAR PCB dizaynini o'rganmoqchi bo'lganlar uchun juda foydali va oson qo'llanma boshlanadi

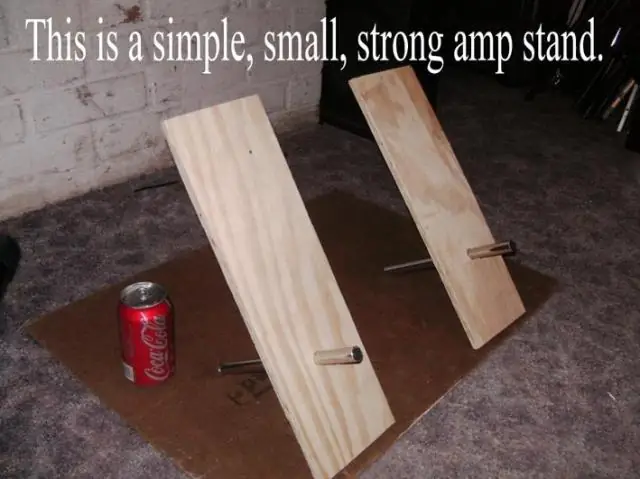

Gitara kuchaytirgichli stend - "Afrika stullari" dizayni - oddiy, kichik, kuchli, oson, bepul yoki haqiqiy arzon: 9 qadam

Gitara Amp Tilt Stend - "Afrika stul" dizayni - Oddiy, Kichik, Kuchli, Oson, Bepul yoki Haqiqiy Arzon: Gitara Amp Tilt Stend - Juda oson - oddiy, kichik, kuchli, bepul yoki haqiqiy arzon. Barcha o'lchamdagi amperlar uchun, hatto alohida boshli katta shkaflar. Faqat kerakli o'lchamdagi taxtalar va quvurlarni tayyorlang va sizga kerak bo'lgan deyarli barcha uskunalar kerak bo'ladi