Mundarija:

- Muallif John Day day@howwhatproduce.com.

- Public 2024-01-30 13:23.

- Oxirgi o'zgartirilgan 2025-01-23 15:14.

AmCoder tomonidan https://www.linkedin.com/in/mituFollow Muallifning boshqa ma'lumotlari:

Haqida: Mitu Raj - shunchaki havaskor va o'quvchi - chip dizayneri - dasturiy ta'minot ishlab chiqaruvchisi - fizika va matematika ixlosmandlari AmCoder haqida ko'proq ma'lumot »

## Bu sinus va kosinus to'lqinini hosil qilish uchun CORDIC ALGORITHM ni VHDL orqali amalga oshirish uchun Google -da eng ko'p bosilgan, ommabop havola ## Hozirgi vaqtda ko'plab apparat -samarali algoritmlar mavjud, biroq ular dasturiy tizimlarning ustunligi tufayli yaxshi ma'lum emas. ko'p yillar. CORDIC - bu algoritm bo'lib, u ko'p funktsiyalarni, shu jumladan ba'zi trigonometrik, giperbolik, chiziqli va logarifmik funktsiyalarni hisoblash uchun ishlatiladigan siljish va qo'shish majmuasidan boshqa narsa emas. Bu kalkulyatorda ishlatiladigan algoritm va hokazo. Shunday qilib, oddiy o'zgartirgichlar va qo'shimchalar yordamida biz korporativ algoritm yordamida DSP kuchi kam bo'lgan uskunani loyihalashimiz mumkin. Shunday qilib, uni VHDL yoki Verilog -da yalang'och RTL dizayni sifatida maxsus suzuvchi nuqta birliklari yoki murakkab matematik IP -dan foydalanmasdan loyihalash mumkin.

1 -qadam: VHDL va Modelsim

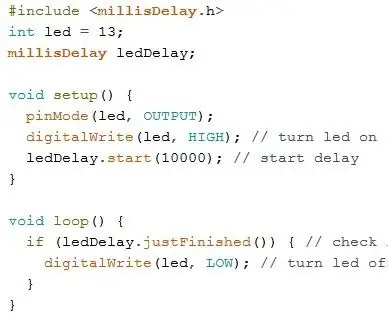

Bu erda kordik algoritm sinus to'lqin va koz to'lqinini yaratish uchun VHDL yordamida amalga oshiriladi. Sinus va kirish burchagi kosinusini juda aniq chiqarishi mumkin. Kod FPGA -da sintez qilinadi. Modelsim dizayn va sinov dastgohini taqlid qilish uchun ishlatiladi.

2 -qadam: Dizayn va sinov stoli uchun VHDL kodi

Ikkilamchi o'lchov usuli suzuvchi nuqta raqamlarini ifodalash uchun ishlatiladi.

Iltimos, kodlashdan oldin ilova qilingan hujjatlar orqali o'ting.

O'tish thruSimulating cordic_v4.vhd - Dizayn - Kirish - 32 bitli burchak + belgi biti; 0 dan +/- 360 gradusgacha bo'lgan har qanday burchakni 0,000000000233 darajali aniqlik bilan ishlov bera oladi. Kirish paytida -> MSB -bu belgi biti, qolgan 32 bit esa kattalikni bildiradi. aniqlik bilan 0.00001526. E'tibor bering, agar sinus yoki cos qiymati manfiy bo'lsa, chiqish 2 ning iltifot shaklida ko'rsatiladi. Testb.vhd simulyatsiyasi - Dizayn uchun sinov dastgohi (1) Kirish burchaklari va tortishish reset = '0'. Simulyatsiyaning ikki bosqichidan so'ng "1" holatiga qaytaring va "hammasini ishga tushiring." to'g'ri.

3 -qadam: fayllar biriktirilgan

(1) cordic_v4.vhd - Dizayn. (2) testb.vhd - Dizayn uchun sinov dastgohi.

(3) Burchakli kirishni majburlash va ikkilik natijalarni konvertatsiya qilish bo'yicha hujjat.

Yangilash: Bu fayllar eskirgan va boshqa ko'rsatilmagan. ILTIMOSI QADAMDAN FAYLLARNI QO'LLANING

4 -qadam: Mini -kordik IP yadrosi - 16 bit

Yuqoridagi dasturni cheklash- sekin, past chastotali ish chastotasi, chunki bitta soat tsiklida hisob-kitoblar amalga oshiriladi. Mini-Cordic IP Core- 16 bit

- Ish faoliyatini yaxshilash uchun bir necha tsikllarga taqsimlangan tanqidiy yo'llar.- Tezroq- FPGA tomonidan tasdiqlangan dizayni 100 MGts soatgacha sintezlangan.- Ko'proq maydon HDL-da optimallashtirilgan, Kamroq apparat.- Yuklanish va bajarilgan holat signallari. oldingi. Testbench:

0 dan 360 graduslik burchakli kirishlar to'liq avtomatlashtirilgan

Ilova qilingan fayllar: 1) mini -kordik asosiy vhdl fayli2) mini -kordik sinov dastgohi 3) Mini -kordik IP -yadro qo'llanmasi 4) Burchaklarni qanday majburlash va natijalarni o'zgartirish haqida hujjat.

Barcha savollar uchun men bilan bog'laning:

Mitu Raj

meni kuzatib boring:

pochta: iammituraj@gmail.com

### Jami yuklab olishlar: 325 01-05-2021 gacha ###

### Kod oxirgi tahrir qilingan: 20.07.2020 ###

Tavsiya:

DIY -- Arduino Uno yordamida smartfon yordamida boshqariladigan o'rgimchak robotini qanday yasash mumkin: 6 qadam

DIY || Qanday qilib Arduino Uno yordamida smartfon yordamida boshqariladigan o'rgimchak robotini yasash mumkin: O'rgimchak robotni yaratishda robototexnika haqida ko'p narsalarni bilib olish mumkin. Bu videoda biz sizga o'rgimchak robotini yasashni ko'rsatamiz, uni biz o'z smartfonimiz yordamida boshqaramiz (Androi

Arduino va DFPlayer Mini MP3 pleer moduli yordamida LCD yordamida MP3 pleerni qanday yasash mumkin: 6 qadam

Arduino va DFPlayer Mini MP3 pleer moduli yordamida LCD yordamida MP3 pleerni qanday yasash mumkin: Bugun biz Arduino va DFPlayer mini MP3 pleer moduli yordamida LCD bilan MP3 pleer yasaymiz. Loyiha SD -kartadagi MP3 fayllarni o'qishi va pauza qilishi mumkin. va 10 yil oldingi qurilma bilan bir xil o'ynang. Bundan tashqari, oldingi qo'shiq va keyingi qo'shiq qiziqarli bo'ladi

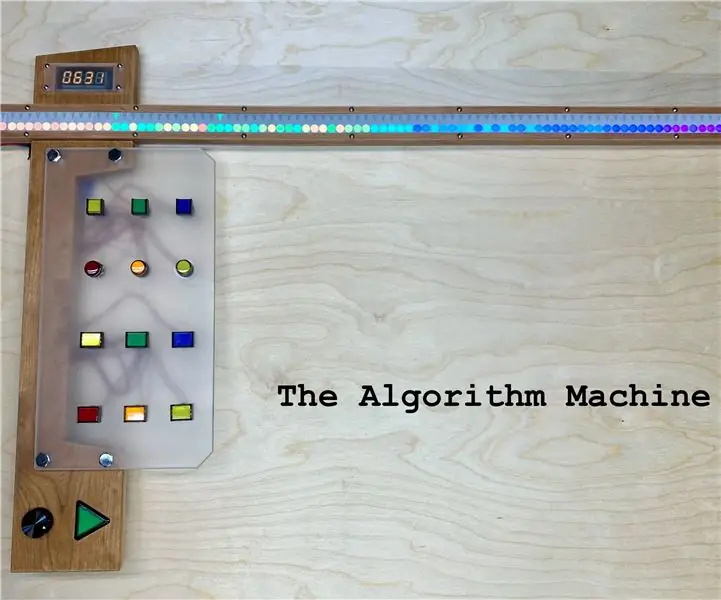

Algoritm mashinasi: 13 qadam (rasmlar bilan)

Algoritm mashinasi: Men 15 yildan buyon kollej darajasida informatika fanidan dars beraman va mening tajribam dasturlash sohasida bo'lsa -da, men qidirish va saralash uchun standart algoritmlarni o'rganishga ko'p vaqt sarflayman. O'qitish nuqtai nazaridan

VHDL va Basys3 taxtasi yordamida asosiy sekundomer: 9 qadam

VHDL va Basys3 taxtasidan foydalanadigan asosiy sekundomer: Asosiy VHDL va Basys 3 taxtasi yordamida sekundomerni yaratish bo'yicha ko'rsatmaga xush kelibsiz. Siz bilan loyihamizni bo'lishishdan xursandmiz! Bu 2016 yilning kuzida, Cal Poly, SLOda o'tkaziladigan CPE 133 (Raqamli dizayn) kursining yakuniy loyihasi edi. Biz qurayotgan loyiha

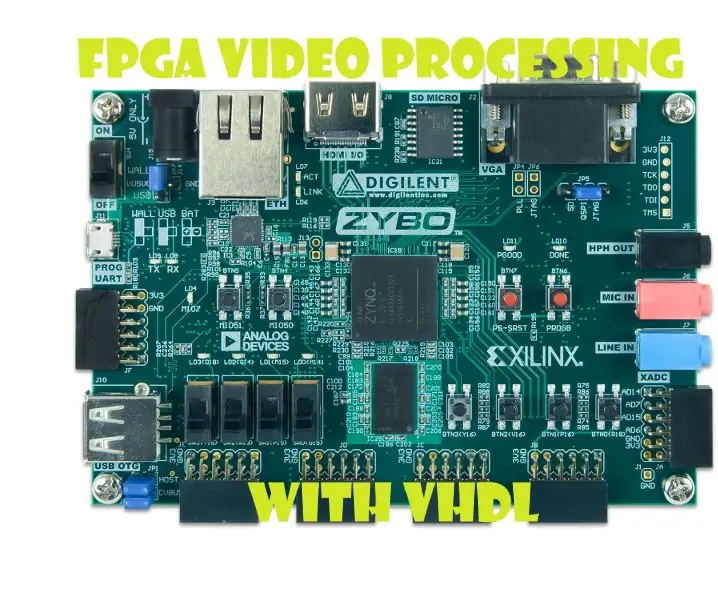

VHDL va Zybo yordamida videoni qayta ishlash: 10 qadam

VHDL va Zybo yordamida videoni qayta ishlash: FPGA protsessorlari protsessorlarga qaraganda tezroq ishlaydi, chunki ular parallel ravishda ko'plab hisob -kitoblarni amalga oshirishlari mumkin. Eslatma: Bu loyiha hozircha qurilish bosqichida va takomillashmoqda (menda vaqt bor). Ayni paytda men dunyo bo'ylab sayohat qilaman