Mundarija:

- Muallif John Day day@howwhatproduce.com.

- Public 2024-01-30 13:25.

- Oxirgi o'zgartirilgan 2025-01-23 15:14.

Men bu blogda olgan javoblarimdan ko'nglim to'ldi. Mening blogimga tashrif buyurganingiz va o'z bilimlarimni siz bilan bo'lishishga undaganingiz uchun rahmat. Bu safar men barcha SOClarda ko'riladigan yana bir qiziqarli modul - Interrupt Controller dizaynini taqdim etaman.

Biz oddiy, ammo kuchli dasturlashtiriladigan uzilishlar boshqaruvchisini loyihalashtiramiz. Bu platformalar bo'ylab ko'chirilishi mumkin bo'lgan to'liq sozlanadigan va parametrlangan dizayn. Men buni NVIC, 8259a, RISC-V PLIC, Microblaze-ning INTC va boshqalar kabi mashhur interrupt-kontroller arxitekturasini ko'p o'qiganimdan so'ng ishlab chiqdim. Umid qilamanki, siz bu blogni foydali deb bilasiz va protsessor uzilishlarni qanday boshqarishini bilib olasiz. uzilish tekshiruvi yordamida.

1 -qadam: Xususiyatlar

IP -ning texnik xususiyatlari quyidagilar:

- AHB3-Lite interfeysi.

-

Statistik sozlanishi parametrlar:

- Tashqi uzilish manbalari soni; 63 ta uzilishni qo'llab -quvvatlaydi.

- Ustuvorlik darajasi; 63 darajagacha qo'llab -quvvatlaydi.

- Uyalash darajalari soni; 8 darajagacha uyalashni qo'llab -quvvatlaydi.

- Avtobus kengligi; 32 yoki 64.

- Global va mahalliy maskalanadigan uzilishlar.

- Har bir uzilish uchun dinamik sozlanadigan ustuvorlik darajasi.

- Ikkita ish tartibi - To'liq joylashtirilgan rejim va Teng ustuvorlik rejimi.

- Faol yuqori darajadagi sezgir uzilishlarni qo'llab-quvvatlaydi.

Dizaynda RISC-V PLIC spetsifikatsiyalari ilhomlangan qo'l uzish mexanizmi ishlatiladi.

Oldindan uzilish 8259a dan ilhomlangan

Boshqa o'qishlar: Microblaze INTC, NVIC

2 -qadam: PIC haqida umumiy ma'lumot

Dasturlashtiriladigan uzilishlarni boshqarish moslamasi (PIC) tashqi periferiya qurilmalaridan bir nechta uzilishlarni qabul qiladi va ularni maqsadli protsessor yadrosiga bitta uzilish chiqishiga birlashtiradi.

PIC nazorat va holat registrlari orqali boshqariladi. Barcha PIC registrlari xotira xaritasi bo'lib, ularga AHB3-Lite avtobus interfeysi orqali kirish mumkin.

Ro'yxatga olish banki konfiguratsiya registri, yoqish registrlari, kutilayotgan registrlar, xizmat ko'rsatuvchi registrlar, ustuvor registrlar va ID registridan iborat bo'lib, ular Interrupt Controller-ga xosdir.

Konfiguratsiya registri PIC ish rejimini o'rnatish uchun ishlatiladi. U to'liq ichki rejimda yoki teng ustuvorlik rejimida ishlashi mumkin.

Har bir tanaffusga ustuvorliklar berilishi va alohida niqoblanishi mumkin. Barcha uzilishlarni global maskalash ham qo'llab -quvvatlanadi.

Ro'yxatga oluvchi bank Priority Resolver va BTC (Binary-Tree-Comparator) bilan o'zaro aloqada bo'lib, kutilayotgan uzilishlarning ustuvorliklarini hal qiladi va shunga mos ravishda protsessorga uzilishni tasdiqlaydi. ID reestri kutilayotgan uzilishlar uchun eng ustuvor identifikatorni o'z ichiga oladi.

3 -qadam: RTLni loyihalash va amalga oshirish

PICning dizayndagi ustuvorliklarini hal qilishning kechikishini kamaytirish, bu dizaynning eng muhim qismi. Dizayn ustuvorliklarni bitta soat tsiklida hal qilganligi sababli, Log2 murakkabligi bo'lgan manbalar sonining ko'payishi bilan ishlash yomonlashadi.

Dizayn muvaffaqiyatli amalga oshirildi va Artix-7 FPGA-da quyidagi chastotalarga qadar vaqt tekshirildi.

- 15 ta manbaga qadar: 100 MGts

- 63 ta manbaga qadar: 50 MGts

Faqat PIC tomonidan qo'shilgan uzilish kechikishi - 3 soatlik tsikl (Protsessorning kontekstli o'tish vaqti va ISR buyrug'ini qabul qilish vaqtidan tashqari).

4 -qadam: Muhim eslatmalar va biriktirilgan fayllar

Muhim eslatmalar:

- Agar AHB3-Lite interfeysi kerak bo'lmasa, siz yuqori modulni o'zgartirishingiz va PIC skeletlari topildi dizaynidan foydalanishingiz mumkin. Biroq, taqdim etilgan test stoli AHB3-Lite interfeysi bilan IP uchun mo'ljallangan.

- PIC IP v1.0 - bu butunlay ko'chma, yalang'och RTL dizayni.

- Ikkala rejimda ishlash uchun funktsional tasdiqlangan.

Qo'shilgan fayllar:

- Dizayn kodlari va VHDL -dagi test stoli.

- To'liq IP -hujjatlar.

Bu ochiq manba kodli dizayn … Foydalanishda bemalol …

Har qanday so'rov uchun, istalgan vaqtda:

Mitu Raj

Tavsiya:

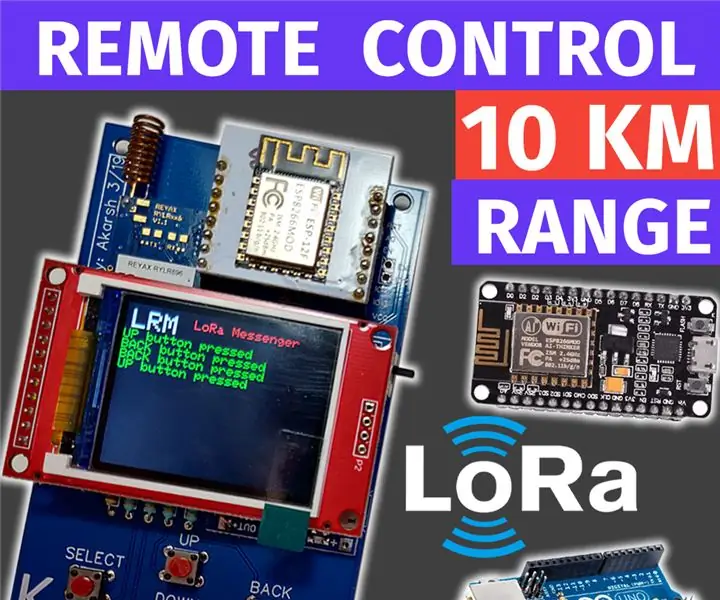

LoRa asosidagi masofadan boshqarish pulti - Katta masofadan asboblarni boshqarish: 8 qadam

LoRa asosidagi masofadan boshqarish pulti | Katta masofadan asboblarni boshqarish: Hey, nima bo'ldi, bolalar! Bu loyihada biz LEDlar, motorlar kabi turli xil asboblarni boshqarish uchun ishlatilishi mumkin bo'lgan masofadan boshqarish pultini yaratmoqchimiz yoki agar biz kundalik hayotimiz haqida gapiradigan bo'lsak, biz o'z uy dasturchimizni boshqaramiz.

Asosiy parametrlarni avtomatlashtirilgan boshqarish bilan akvarium dizayni: 4 qadam (rasmlar bilan)

Asosiy parametrlarni avtomatlashtirilgan boshqarish bilan akvarium dizayni: Kirish Bugun dengiz akvariumiga g'amxo'rlik qilish har bir akvarist uchun mavjud. Akvarium sotib olish muammosi qiyin emas. Ammo aholining to'liq hayotini ta'minlash, texnik nosozliklardan himoya qilish, oson va tez parvarishlash va parvarish qilish uchun

VHDLda I2C Master dizayni: 5 qadam

VHDL -dagi I2C Master -ning dizayni: VHDL -dagi oddiy I2C -master loyihasi muhokama qilinadi. Eslatma: to'liq tasvirni ko'rish uchun har bir tasvirni bosing

VHDLda SPI Master dizayni: 6 qadam

VHDL -dagi SPI ustasi dizayni: VHDL -da biz noldan SPI avtobus ustasini loyihalashtiramiz

VHDLda UART dizayni: 5 qadam

VHDL -dagi UART dizayni: UART universal asenkron qabul qilgich uzatuvchi degan ma'noni anglatadi. Bu eng ommabop va oddiy ketma -ket aloqa protokoli bo'lib, siz VHDLda UART modulini loyihalashni o'rganasiz